LogicWorks

This document describes procedures to program PROMs (Programmable ReadOnly Memory). The PROMs are programmed using data in a

Tutorial on how to build custom parts for your circuits in LogicWorks. Introduces circuit hierarchy in schematic capture. Logicworks Corporation provides managed hosting and cloud computing services. It offers private, public, and hybrid cloud solutions. Additionally, the company provides healthcare cloud solutions, including HIPAA compliant infrastructure; disaster recovery for electronic medical record (EMR) and electronic health record (EHR) platforms; medical.

25 Years of Cloud Expertise. Logicworks has been helping customers achieve IT operational excellence and cloud compliance for over 25 years. Our innovative platform, dedicated certified engineers, and decades of traditional IT experience combine to enable our. 1 LogicWorks 5 INTERACTIVE CIRCUIT DESIGN SOFTWARE REFERENCE MANUAL Capilano Computing Systems Ltd. North Vancouver, Canada LW Reference.bk Page 1 Monday, December 15, 2003 5:59 PM. (212) 625-5454 sales@logicworks.com Our AWS and Azure Certified Engineers can assess your environment for GDPR, HIPAA, HITRUST, PCI, SOC1, & SOC2. Then remediate to protect against internal & external threats.

file (more precisely, a file in the Intel Hex format). The file canbeloaded into a PROM in LogicWorks (for simulation) or a real EPROM(Erasable Programmable ROM), such as the 2732. The procedure forprogramming a PROM in LogicWorks will be described below.Remember that the HEX file must have lines that begin with colons(':'). If you create a HEX file using the Truth Table program, itwill looklike this:

Delete the first few lines to get the following:

Delete the first few lines to get the following:Using the '.HEX' File toProgram a PROM in LogicWorks

The next three steps are for Logicworks on PCs (it is similar forMac). Assume that the .HEX file is in wiliki.

Step 1. Transfer the '.HEX' file from wiliki to the PC

The SSH Secure File Transfer program, available in the EE 260 Lab(Holmes 451) andthe EE Computer Lab (Holmes 387), transfers files between a local andaremote computer. The local computer is the one you'reusing,and the remote is somewhere else. For our purposes, the remotecomputerwill be wiliki, where the .HEX file is located. A file transfercanbe a download, which goes from remote to local, or an upload,which goes from local to remote.

Start the SSH Secure File Transfer, which will open a window. Under the File menu, select Connect. When the programprompts you for a machine, enter

wiliki.eng.hawaii.edu

Now logon. The window will show your files on the local andremote computers. You can navigate around by pointing andclicking. Youcan also create folders/directories.

Navigate on wiliki until you find your HEX file. Navigate onyour local computer until you find a folder to download the file. Select your HEX file on wiliki. Under the Operation menu,select Download. The file should transfer, and you're done. You can close the connectionby simply exiting or closing the application.

- Start LogicWorks 5. In Holmes 387, LogicWorks 5 can befound in folder 'EE Basic Design' or on the drive K 'eepcserver', underLogicworks 5 (click the logicworks exe file).

- Make sure your own parts 'library' is loaded, so that you canstore your new PROM part in it (click here togeta refresher on how to start a new library):

- Under the Simulation menu, select the 'PLA/PROM/RAM ConstructionWizard.' This will take you through a series of queries:

- Select Type of Device to Build: Select PROM.

- Device Specifications:

- Address Lines: Enter number of inputs*.

- Bits Per Word: Enter number of outputs**.

- Data Entry Method: Select Intel Format Hex File

- Navigate until you find the HEX file, then select.

- Select a name for the PROM, e.g., 'Lab 20 Circuit'

- Select your library to store the PROM.

* Logicworks only allows the number to be powers of2. So you may end up having slightly more inputs than you need. Theextra inputs are the ones corresponding to the most significant bits. Whenusing the circuit, tie these to Ground (0). For example, supposeyouneed 5 inputs but must select 8. This leaves you with a PROM withinputsIn7, In6,... In0. When you use the PROM, connect In7, In6, andIn5to Ground.

** Logicworks only allows the numbers to be powers of 2. You mayendup having slightly more outputs than you need. The extra outputsarethe ones corresponding to the most significant bits. You canignore these. For example, suppose you need 3 outputs but mustselect 4. This leaves you with a PROM with inputs Out3, Out2,Out1, Out0. When youuse the PROM, ignore Out3.

Step 3. Delete your files from the PC if it's not your own. Don'tforget your thumb drive or disks.

Appendix A: Refresher

- Creating a new devices (or parts) library forLogicWorks:

- Open LogicWorks if it's not already.

- The libraries menu should appear on the right side. If not,you can open the menu by clicking the library icon, which is a pictureof a collection of books.

- In the upper right corner of the menu, there's an 'x'. Pointthe mouse there and click the mouse's right button. That should openanother menu where you can create a new library or load existing one.In either chase you must then navigate until you find a location tostore your new library or find the existing library.

Appendix B: Intel Hex File Format

We will be using the IntelHex File format to program Programmable Read Only Memory (PROMs)such as the 2732. The format specifies the memory location of thedata, and the data values itself. In addition, it has informationto check for bit errors. The file is a text file but representing hexadecimal numbers. Ahexadecimal number is a number that has base 16. So each digitcan have one of 16 values, {0, 1, 2, ..., 14, 15}. The digit is asingle symbol. For the values 10, 11, ..., 15, the symbols are'A' = 10, 'B' = 11, 'C' = 12, ..., 'E' = 14, and 'F' = 15. Theletters may be upper or lower case. As an example, thehexadecimal number FA is equal to 15x16 + 10. Hexadecimal numbersare useful to represent binary values because it is easy to convert ahexadecimal number to binary and vice versa. Each hexadecimaldigit represents 4 bits. For example the hexadecimal number 'FA'is equal to the binary number '1111 1010'. To convert ahexadecimal number to binary, just convert each hexadecimal digit toits equivalent 4-bit binary number. To convert a binary number tohexadecimal, just partition the binary number into 4-bit chunksstarting from the right. Then convert the 4-bit values intohexadecimal. For example,101101100010101 = 101 1011 0001 0101 = 5 B 1 5. Note that a byte (8bits) is represented by two hexadecimal digits. Also, hexadecimalnumbers are often prefixed by '0x' to indicate it is a hexadecimalnumber, e.g., 0x5B15

The Intel Hex File Format is list of 'lines', where each line either (i) specifies data values at aparticular memory location or (ii)its a line indicating that its the end of the file. Each line hassix parts to it, where each part is also referred as a'field'.

- The first character in the line is always a colon ':'. Itis the first field, and is referred to as the start code.

- The second field is the bytecount, and is the number of bytes in the data field, which willbe described below. This value is typically either 16 or32. It is represented as two hexadecimal digits. So it iseither '0x10' or '0x20'. For our case, this value will typicallybe 16.

- The third field is a 16-bit addresswhich is represented by 4hexadecimal digits. The address is where the data will bestored in the PROM. For our case, the address will typically be0x0000, 0x0010, 0x0020, ....., which corresponds to the address values0, 16, 32, etc.

- The fourth field is record typewhich indicates whether the line has data or is an end of file. 00 = record type, and 01 = end of file.

- The fifth field is the data,and the number of bytes is specified by the byte count. Typically, the byte count is 16, so the data will be represented by 32hexadecimal digits, where 2 hex digits = 1 byte.

- The fifth field is the checksum,which is a value used to check whether any data is in error. Thecheck sum is a fancy way to data together to produce a 'sum' Thischecksum is stored. To check if the data is still good, the sumis calculated, and if it is different than the sum that is stored, thenwe know there is an error. If the calculated and stored sums havethe same values then it is assumed that there are no errors. Fornow, you don't need to know how this sum is calculated. But thechecksum is a byte = 2 hex digits.

, and a checksum of 21. The second line also has data but starting at address 0x0010, and with a checksum of 0xf0. Thefinal line has a record 01 =end of file, byte count =0x00 = 0, address of 0x0000(since there are no data bytes), and checksum of 0xff.

, and a checksum of 21. The second line also has data but starting at address 0x0010, and with a checksum of 0xf0. Thefinal line has a record 01 =end of file, byte count =0x00 = 0, address of 0x0000(since there are no data bytes), and checksum of 0xff.This specifies that the data to be stored is

Address (hex) Data (hex)

0000 f8

Logicworks Noc

0001 fa

0002 f9

0003 fd

0004 fe

0005 fe

0006 f9

0006 f90007 fa

Logicworks Software

0008 ff

0009 ff

etc

Objectives

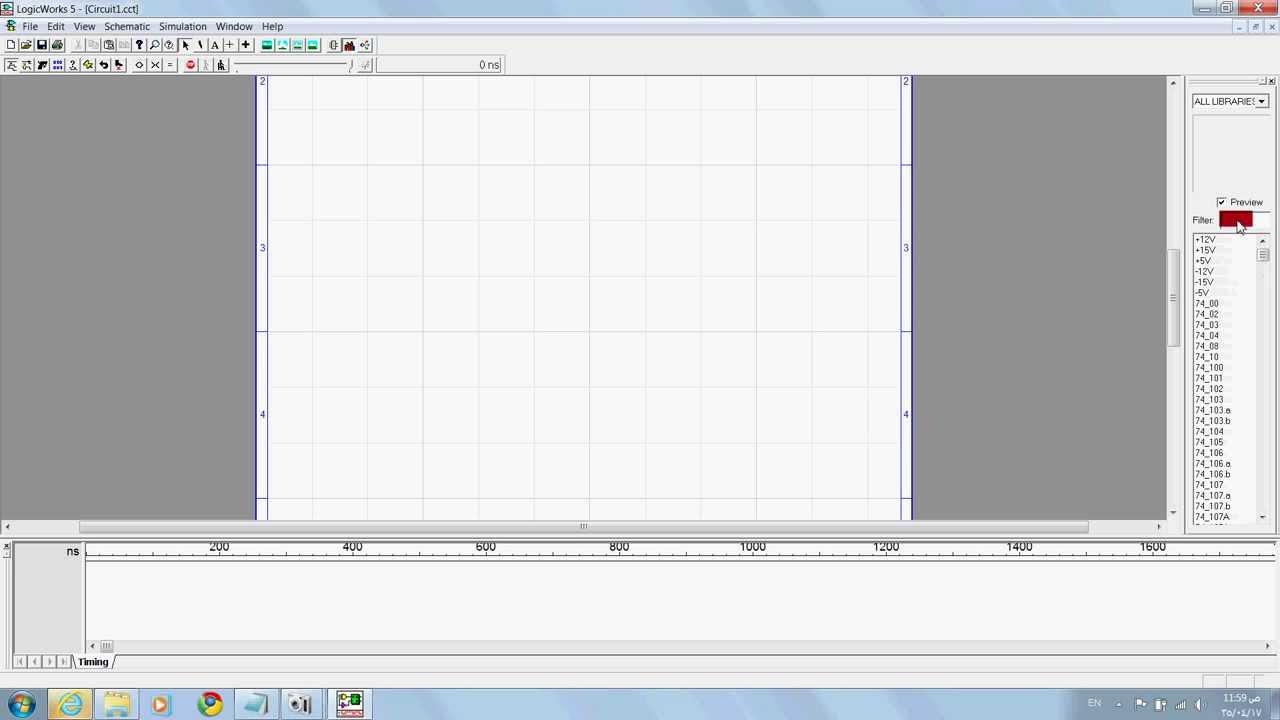

'LogicWorks is an interactive circuit design tool intended for teaching and learning digital logic.' LogicWorks 5 is the newest version of LogicWorks.It is a program that we can use for designing and simulating circuits.

VHDL stands for VHSIC Hardware Description Language. VHSIC means Very High Speed Integrated Circuits.VHDL is an industry-standard language for modeling and synthesizing digital hardware, particularly for programmerable logic or Application SpecificIntegrated Circuits. The VHDL simulation serves as a basis for testing complex designs and validating the design prior to fabrication. As a result,the redesign is reduced, the design cycle is shortened, and the product is brought to market sooner.A VHDL program can be considered as a description of a digital system; the associated simulator will use this description to produce behaviorthat will mimic that of the physical system.

This lab contains the basic structure of VHDL and creating a VHDL model for a device symbol.

1. VHDL Basic Structure

VHDL can be used to describe digital hardware at different levelsof abstraction. It can be used as a tool to enter Boolean equationsand truth tables. Some other techniques will be introduced in the future labs.Entity and Architecture

An entity declaration and an architecture body are the two very basic constructs that are required by every VHDL file. The entity declaration defines the inputs and outputs of the design. The architecture body defines the relationship between the inputs andthe outputs.Example 1:

For this simple circuitwe can use the following VHDL to describe it.Pay attention to the use of entity declaration and architecture body constructs.

Example 2:

We have learnt that a 3-input majority detector has the following truth table:The corresponding Boolean function of it isThe following is the VHDL code to describe this 3-input majority detector.2. Create a VHDL Model for a Device Symbol

- Open LogicWorks 5.

- Close any open circuit diagrams or VHDL files if any.

- Go to the File menu and select the New command.

- In the list of available document types, select Model Wizard and click OK.

- For the Source selection, choose 'Create a new, empty model.'

- For the Destination selection, choose 'Create a new symbol with the specified model attached.'

- Click the Next button.

- Select the VHDL model type, and enter a name, such as, majority3

- Click on the Next button to view the 'Port Interface Panel'.

- Set the Functions to Input. if it isn't already.

- Enter the name a as the first input.

- Click Add Single Bit button.

- Enter the name b, and click the Add Single Bit button again to add the second inpuit.

- Enter the name c, and click the Add Single Bit button again to add the third inpuit.

- Go back to the top of the panel and change the Function selection to Output.

- Enter the name y, and click the Add Single Bit button.

- The port list should now look like this:

- Click on the Next button, you should see this panel.

- If desired, move the pins to different locations on the symbol by dragging and dropping names from one box to another.

- Once you are satisfied with the pin locations, click on the Next button, you should see this panel.

- Click on New Lib button to create a new one on your I: drive, for example I:301mylib.

- Once you have selected a library, click on the Finish button.

- Save majority3.dwv model file in the default location, or find a suitable folder for it.

- Select the New command in the File menu; then choose the Circuit item.

This will creat a new, empty circuit window on the screen. - Locate the majority3 part in the parts list on the right hand side of the screen,

and place it in the circuit window, you should see this part: - Double-click on the majority3 device. This will open the the VHDL model in a new window.

- Refer to Example 2 to get the architecture block completed.

- Compile the VHDL Model.

- Close the majority3 document window, once the file is compiled correctly.

- You should now be looking at the circuit containing majority3 symbol again.

The system description is now complete, so we just have to test it. - Connect a binary switch to a, b, c and a binary probe to y

- Change the values for a, b, c and record the values of the y.

Check if it matches the truth table for the 3-input majority testector. - You should have this circuit.

3. Conclusion

By now, you have learned the basic ideas about VHDL with LogicWorks, but there is much more to learn. This lab material is only an introduction to VHDL with LogicWorks 5. More about VHDL will be introduced in the future labs. There are some LogicWorks 5 manuals available. If you want to work through more tutorials in the manual or want to know more, you can ask me during the lab.You may also ask me questions at lab time or at my office hours in CL119. If a lab requires new features, I will explain more within the lab.

4. Lab Assignments

5. More Info about VHDL

LogicWorks is a trademark of Capilano Computing.

Copyright: Department of Computer Science, University of Regina.